Third Chapter

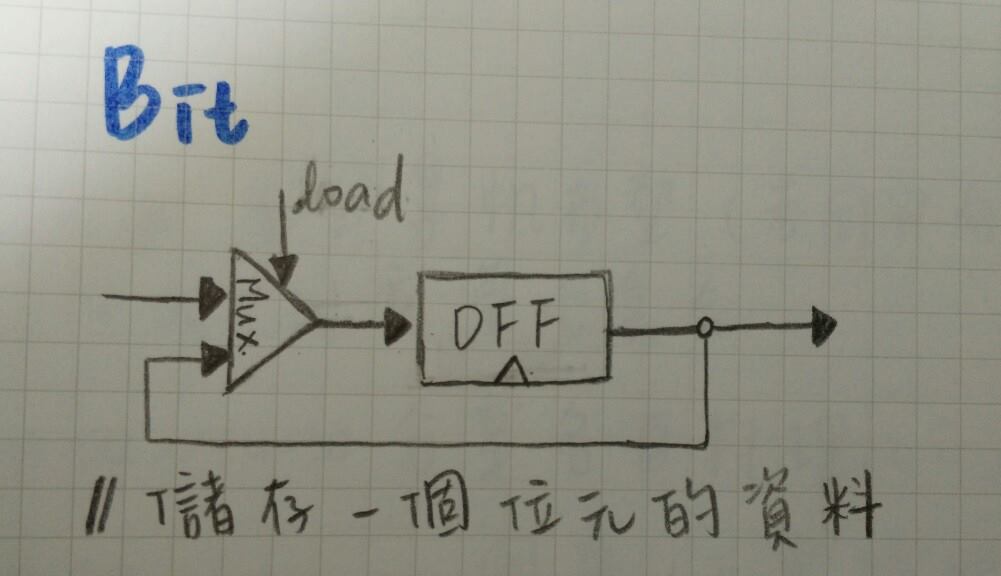

Bit

If load[t]==1 then out[t+1]=in[t] else out[t+1]=out[t]

通過load(t-1)的值決定out(t)是否改變。

CHIP Bit {

IN in, load;

OUT out;

PARTS:

Mux(a=dffout,b=in,sel=load,out=muxout);

DFF(in=muxout,out=dffout);

Or(a=dffout,b=dffout,out=out);

}

Register

CHIP Register {

IN in[16], load;

OUT out[16];

PARTS:

Bit(in=in[0],load=load,out=out[0]);

Bit(in=in[1],load=load,out=out[1]);

Bit(in=in[2],load=load,out=out[2]);

Bit(in=in[3],load=load,out=out[3]);

Bit(in=in[4],load=load,out=out[4]);

Bit(in=in[5],load=load,out=out[5]);

Bit(in=in[6],load=load,out=out[6]);

Bit(in=in[7],load=load,out=out[7]);

Bit(in=in[8],load=load,out=out[8]);

Bit(in=in[9],load=load,out=out[9]);

Bit(in=in[10],load=load,out=out[10]);

Bit(in=in[11],load=load,out=out[11]);

Bit(in=in[12],load=load,out=out[12]);

Bit(in=in[13],load=load,out=out[13]);

Bit(in=in[14],load=load,out=out[14]);

Bit(in=in[15],load=load,out=out[15]);

}

RAM8

CHIP RAM8 {

IN in[16], load, address[3];

OUT out[16];

PARTS:

DMux8Way(in=load, sel=address, a=loadA, b=loadB, c=loadC, d=loadD, e=loadE, f=loadF, g=loadG, h=loadH);

Register(in=in, load=loadA, out=outA);

Register(in=in, load=loadB, out=outB);

Register(in=in, load=loadC, out=outC);

Register(in=in, load=loadD, out=outD);

Register(in=in, load=loadE, out=outE);

Register(in=in, load=loadF, out=outF);

Register(in=in, load=loadG, out=outG);

Register(in=in, load=loadH, out=outH);

Mux8Way16(a=outA, b=outB, c=outC, d=outD, e=outE, f=outF, g=outG, h=outH, sel=address, out=out);

}